After seeing this

project on Make (

or here) I felt like old DRAMs could have a better use... It is a bit sad that so much technology and development by semiconductor engineers and computer designers goes "wasted" on a light box. The light box looks good, don't get me wrong.. but.. so much engineering wasted in a light box... doesn't look right.

I always thought that using these SIMMs in microprocessor applications would be interesting and with the proper memory management it could be used with old 8 bit microprocessors. The likes of Z80, 8085, 6809, 6502 could go with a simple DRAM interface.

Trying to search for information online or even in books, application notes etc is quite elusive, there are three good sources of information:

This one (or here in pdf) is very specific regarding the Z80, and Z180...[...]This one with a PIC processor connected directly to a DRAM chip (source code only).And this one, where a FPGA and a 8051 microcontroller are connected to a 72 pin SIMM. Most of the microprocessor or microcontroller projects online either use one or more large SRAMs (128K,256K and 512K bytes) are these are nowadays readily available.

Although my projects don't need a large RAM size I wanted to probe the use of old SIMMs with the 8085. The Z80 makes it all a bit more simpler because it has been design to use DRAMs, so at the end of the instruction fetch cycle the RFSH and MREQ signals go low, the problem with this that the instruction fetch cycle is slightly (half cycle) shorter (

see here).

It seems logical the one would try to do the same in a different processor, while the processor is decoding and executing the fetched instruction the DRAM controller preforms a DRAM refresh, this way every instruction fetch a refresh is performed which normally is often enough. Except, in the 8085 case, if the processor is halted. The Z80 solved this problem by still performing instruction fetches during HALT (it executes NOPs). I decided to carry on accepting this problem and do not write any programs that halt to processor unless I want to lose the contents of the DRAM.

In the 8085 there's no refresh cycle, but at the end of every instruction fetch, during 1 to 3 cycles (depending on the instruction just fetched), the CPU relinquishes the bus, these are called T4,T5 and T6 states (see

here). Although a single cycle for refresh might not seem a lot, one could extend the cycle a bit more until ALE goes high, from then on the address on the bus is valid and a normal fetch should be made.

The 8085 does have an slight advantage when compared to the Z80 (and Z8000), the read signal and write signal (RD and WR) are active for the same time weather in instruction fetch, memory read and or memory write (and even I/O these are extended in the Z80), so there's no need for a early-write signal when using the SIMMs.

I designed the circuit as a combination of two sequential circuits, one generating RAS, CAS and Address inputs during a normal read/write and instruction fetch (accessing), and another circuit for refreshing the RAM on every instruction fetch (refreshing). During a instruction fetch from a non-selected memory the last cycle is used to do a CAS before RAS refresh, if the fetch is done from the DRAM, the access cycle is extended to do a hidden refresh (toggle of RAS line while CAS is low). When ALE goes high all DRAM access activities stop and the circuit waits for RD or WR to go low to start the RAS/Address Mux/ CAS sequence. I use the X2 output from the 8085 because it is at 2 times the CLK output, therefore it allows faster state switching and a longer memory access time.

I've designed and assembled the circuit and I'm about to do extensive testing if it really works or not. Here's the schematic of the CAS/RAS generation, the connection to the SIMM is straight forward, the pin-out of a 30-pin SIMM is

here, and some of the history of SIMM development is

here.

The 8085 is clocked at 8MHz, and on the oscilloscope RAS appears on top and CAS on the bottom. My only problem has been my EPROM emulator, and I need to do something about that in the future. It is only working in DOS... So now I need to do all the programming in DOS and test the system with the oscilloscope. I'm also using the SOD line to trigger the oscilloscope when the SIM instruction is executed, the current program is the following (beware, 8085 assembly follows):

.title test_program 0

.sbttl testing

.area ram(abs,cseg)

.org 0x0000

reset:

di

lxi h,0xC000

lp000:

mvi a,#0xC0

sim

mov a,m

jmp lp001

lp001:

mvi a,#0x40

sim

mov m,a

jmp lp000

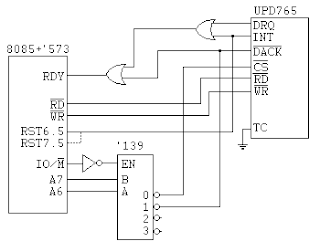

I think that I am finally setting for a 8085 at 8Mhz connected to a upd765 and a software UART with SID, SOD and RST5.5 lines, memory will probably be 64K SRAM (w/ 32K paged in/out) and a 32k ROM. An ON/OFF switch, a RESET, a TRAP and a RST7.5 interrupt push switches.

I think that I am finally setting for a 8085 at 8Mhz connected to a upd765 and a software UART with SID, SOD and RST5.5 lines, memory will probably be 64K SRAM (w/ 32K paged in/out) and a 32k ROM. An ON/OFF switch, a RESET, a TRAP and a RST7.5 interrupt push switches.