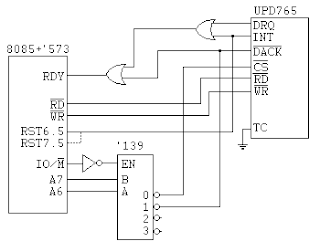

After reading about lots of complaints about small disk sizes I decided to go the extra mile and implement the said pseudo-dma circuit and routine for 3.5 HD drives. Yes, I had to ask some more questions in the yahoo group, but someone with infinite patience explained me the easy way to do it. Here is the schematic I used for pseudo-dma and the 8085 to read 3.5 HD floppies.

The operation of this circuit is the following, the read operation is started and a special IN instruction (addresses 2xH) lock the processor in a wait state and asserts DACK. When the byte is ready (this can last a full rotation of the disk) DRQ is asserted unlocking the processor and completing the read.

There is a problem with this schematic and my program, if an interrupt occurs during a normal read (signaling an error during the read) the processor is unlocked but the first byte read is already the result byte. Beeing RST6.5 level triggered, when the next instruction to the IN is fetched there is no longer a pending interrupt (765 INT line gets deasserted when the first byte of result phase is read) and the system hangs in execution phase.

One alternative would be to use RST7.5, it is latched by the processor, but on entry in the interrupt routine one should be aware that ACC could contain the first result phase byte. There is a special case where it could not be! As in an error occurs exactly after reading a byte.

The big issue is that a read or write during execution phase must be completed at 16us nominal (13-11us worst case) and testing if byte is ready or interrupt is pending takes time.

My next "development" will be polling interrupts for seek and recalibrate operations, as for the execution phase, maybe go back to the NO DMA mode (ND=1) and use HALT as a wait for interrupt instruction, do the test for results phase and read in the byte.

As for a latter hardware development would be to reduce the 765 clock from 8MHz to 4MHz and use CLKOUT instead of X2 buffered (save a gate).

No comments:

Post a Comment